- 您现在的位置:买卖IC网 > Sheet目录1991 > CS4341-CZZ (Cirrus Logic Inc)IC DAC STER 24BIT 96KHZ 16TSSOP

CS4341

18

DS298F5

4.2.2

External Serial Clock Mode

The device will enter the External Serial Clock Mode whenever 16 low to high transitions are de-

tected on the SCLK pin during any phase of the LRCK period. The device will revert to Internal

Serial Clock Mode if no low to high transitions are detected on the SCLK pin for 2 consecutive pe-

riods of LRCK.

4.3

Digital Interface Format

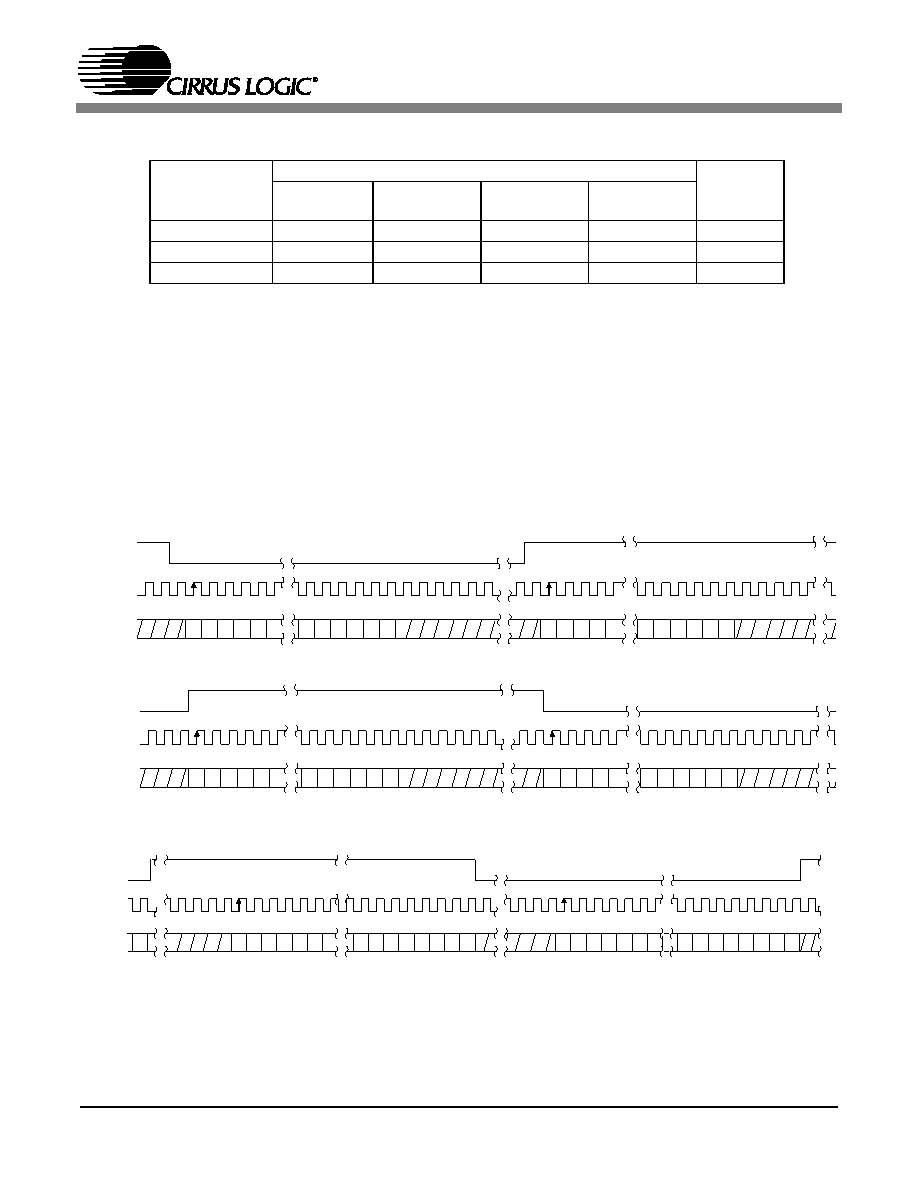

The device will accept audio samples in several digital interface formats. The desired format is selected

via the DIF0, DIF1 and DIF2 bits in the Mode Control register (see section 6.2.2). For an illustration of the

Input

Digital Interface Format Selection

Internal

MCLK/LRCK

Ratio

I2S up to 16 or

24 Bits

Left Justified 24

Bits

Right Justified

18, 20 or 24 Bits

Right Justified

16 Bits

SCLK/LRCK

Ratio

512, 256, 128

(Format 1)

-

X

32

384, 192

XX

X

48

512, 256, 128

(Format 0)

X

-

64

Table 4. Internal SCLK/LRCK Ratio

LR C K

SC L K

Left C ha nnel

R ig h t C ha n nel

SDATA

+3 +2 +1

+5 +4

MSB

-1 -2 -3 -4 -5

+3 +2 +1

+5 +4

-1 -2 -3 -4

LSB

MSB

LSB

Figure 17. CS4341 Formats 0-1 - IS up to 24-Bit Data

LR C K

SC L K

Left C ha nnel

R ig h t C ha n nel

SDATA

+3 +2 +1

+5 +4

MSB

-1 -2 -3 -4 -5

+3 +2 +1

+5 +4

-1 -2 -3 -4

LSB

MSB

LSB

Figure 18. CS4341 Format 2 - Left Justified up to 24-Bit Data

LRCK

SCLK

Left C hannel

SDATA

+6 +5 +4 +3 +2 +1

+7

-1 -2 -3 -4 -5

LSB

R ight Cha nnel

MSB

LSB

+6 +5 +4 +3 +2 +1

+7

-1 -2 -3 -4 -5

MSB

LSB

Figure 19. CS4341 Formats 3-6 - Right Justified

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CS4341A-KSZ

IC DAC STER 24BIT 192KHZ 16SOIC

CS4351-DZZ

IC DAC STER 112DB 192KHZ 20TSSOP

CS4352-DZZ

IC DAC STER 102DB 192KHZ 20TSSOP

CS4354-CSZ

IC DAC 24BIT SRL 14SOIC

CS4360-KZZ

IC DAC STER 6CH 102DB 28TSSOP

CS4361-CZZR

IC DAC STER 6CH 105DB 20-TSSOP

CS4362-KQZ

IC DAC 6CH 114DB 192KHZ 48LQFP

CS4362A-DQZ

IC DAC 6CH 114DB 192KHZ 48-LQFP

相关代理商/技术参数

CS4341-CZZR

功能描述:数模转换器- DAC IC 24bit 96kHz 101dB Stereo DAC w/VC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

CS4341-KS

功能描述:数模转换器- DAC 24-bit 96kHz 101dB Stereo DAC w/VC

RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

CS4341-KSR

功能描述:数模转换器- DAC 24-bit 96kHz 101dB Stereo DAC w/VC

RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

CS4341-KSZ

制造商:Cirrus Logic 功能描述:24-BIT, 96 KHZ STEREO DAC WITH VOL CNTRL - Bulk 制造商:Cirrus Logic 功能描述:IC DAC 24BIT SRL 96KHZ 16-SOIC 制造商:Cirrus Logic 功能描述:24Bit 96kHz 101dB Stereo DAC

CS4341-KSZR

制造商:Cirrus Logic 功能描述:DAC DUAL DELTA-SIGMA 24BIT 16SOIC - Tape and Reel

CS4344

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:10-PIN, 24-BIT, 192KHz STEREO D/A CONVERTER

CS4344_05

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:10-PIN, 24-BIT, 192KHz STEREO D/A CONVERTER

CS4344-CZZ

功能描述:音频数/模转换器 IC Stereo DAC 24-Bit 192kHz RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel